ic工具虚拟机:现代集成电路设计与验证的核心引擎

在当今信息技术飞速发展的时代,集成电路(IC)作为电子设备的“大脑”,其设计与验证的复杂度呈指数级增长,为应对这一挑战,IC工具虚拟机(IC Tool Virtual Machine)应运而生,它通过虚拟化技术为IC设计流程提供了灵活、高效且隔离的运行环境,成为推动半导体产业创新的关键基础设施,本文将从技术原理、核心优势、典型应用及未来趋势四个维度,深入探讨IC工具虚拟机的价值与意义。

技术原理:虚拟化赋能IC工具的底层支撑

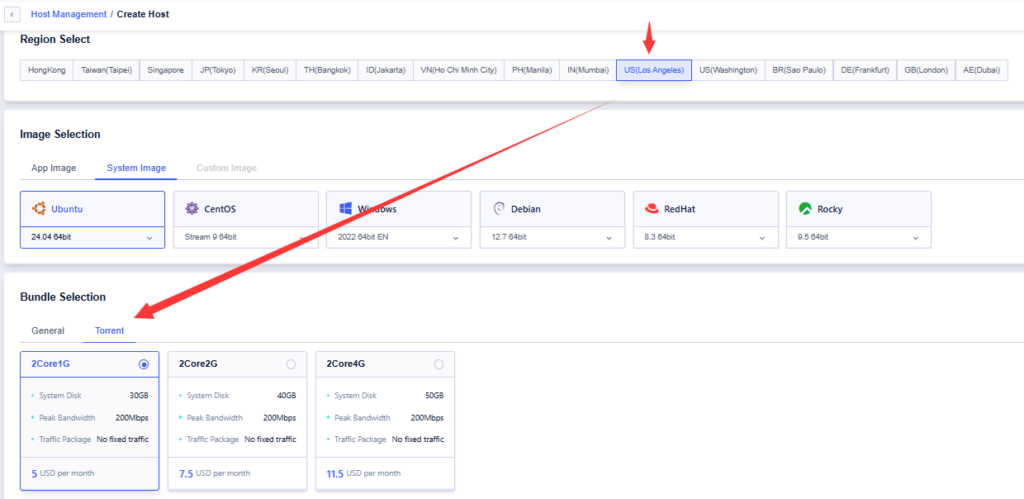

IC工具虚拟机本质上是一种基于虚拟化技术的运行环境,其核心在于将物理硬件资源(如CPU、内存、存储及网络)抽象为虚拟资源,再为不同的IC设计工具(如EDA软件、仿真器、验证平台等)提供独立的、隔离的运行空间,其技术架构通常分为三层:

- 硬件层:由高性能服务器或集群组成,提供计算、存储和网络等基础资源。

- 虚拟化层:采用Type-1(裸金属)或Type-2(宿主型) hypervisor(如KVM、VMware ESXi),实现资源池化与动态调度,确保多个虚拟机(VM)并行运行时互不干扰。

- 工具层:在虚拟机内部部署操作系统(如Linux)及IC设计工具链,例如Synopsys的VCS、Cadence的Xcelium,或开源工具如GHDL、Icarus Verilog。

通过这种分层架构,IC工具虚拟机实现了“工具与硬件解耦”,使得设计工具可在不同物理环境中保持一致的行为,同时充分利用硬件资源的多核并行能力,大幅提升设计效率。

核心优势:从效率到安全的全方位提升

相较于传统本地部署的IC工具环境,虚拟化模式带来了显著优势,主要体现在以下四个方面:

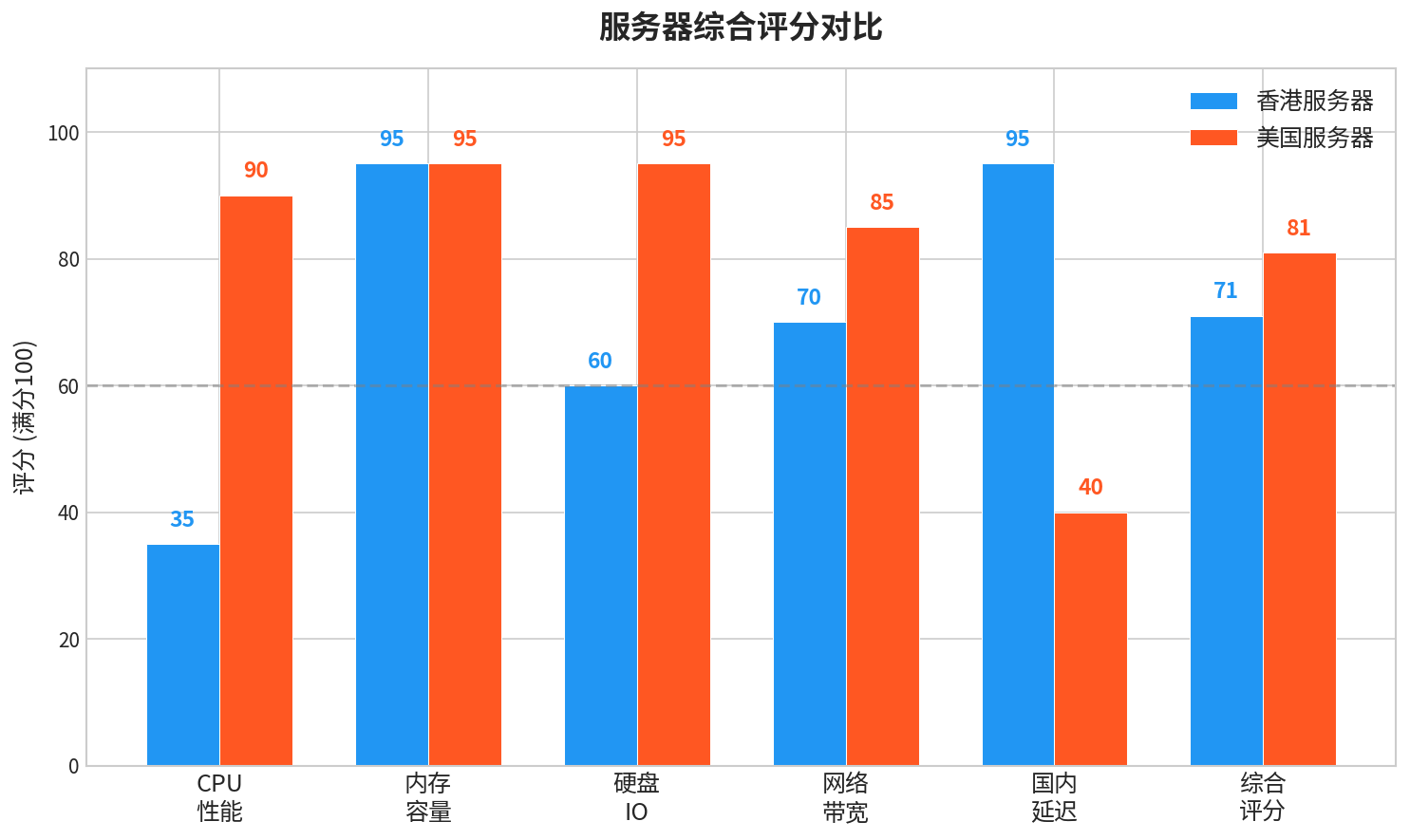

资源利用率最大化

IC设计流程(如逻辑综合、布局布线、仿真验证)对计算资源需求极高,且不同阶段资源负载差异巨大,虚拟机支持资源的动态分配与弹性伸缩,可根据任务需求实时调整CPU、内存等资源,避免传统“一工具一服务器”模式下的资源闲置,提升硬件利用率30%以上。

环境隔离与一致性

IC设计工具常依赖特定的操作系统版本、库文件及驱动程序,环境冲突可能导致工具异常,虚拟机通过完全隔离的运行环境,为每个工具或项目提供独立的“沙箱”,确保环境配置的一致性与可复现性,不同团队可同时运行不同版本的EDA工具,无需担心依赖冲突。

成本与运维优化

企业无需为每个工具配置高性能物理服务器,而是通过虚拟化集中管理资源,降低硬件采购成本,虚拟机的快照、克隆功能简化了环境部署与版本回滚,运维人员可快速搭建测试环境,减少80%以上的环境配置时间。

安全性与合规性

敏感的IC设计数据(如芯片架构、源代码)可通过虚拟机加密存储与网络隔离,防止未授权访问,虚拟机支持细粒度的权限控制,确保不同角色(如设计工程师、验证团队)仅能访问授权资源,满足企业对数据安全与合规性的要求。

典型应用:覆盖IC设计全生命周期

IC工具虚拟机已深度融入IC设计的各个环节,从前端验证到后端实现,再到量产支持,均发挥着不可替代的作用:

前端设计与仿真验证

在芯片设计初期,工程师需通过仿真验证逻辑功能的正确性,虚拟机可部署大规模并行仿真环境(如基于SystemVerilog的UVM验证平台),利用多核CPU加速仿真进程,缩短验证周期,在5G基带芯片设计中,虚拟机集群可将千万门级电路的仿真时间从数周压缩至数天。

后端物理实现

布局布线(P&R)工具(如Cadence Innovus、Synopsys IC Compiler)对内存与存储性能要求极高,虚拟机通过高速NVMe存储分配与大内存支持,确保工具高效处理复杂的布局数据,虚拟机的热迁移功能可在服务器维护时无缝切换任务,避免设计中断。

云原生与协同设计

随着半导体产业向全球化协作转型,云原生IC设计平台逐渐兴起,虚拟机作为云环境中的核心载体,支持跨地域团队共享设计资源与工具,实现“设计上云”,AWS Semiconductor Cloud、阿里云IC设计加速平台均基于虚拟化技术,为客户提供弹性、低成本的IC设计服务。

教育与培训

高校与企业培训中,虚拟机可快速搭建标准化的IC学习环境,学生无需配置本地硬件即可接触专业EDA工具,降低学习门槛,MIT、清华大学等高校已通过虚拟化实验室,为学生提供从数字逻辑设计到芯片验证的全流程实践平台。

未来趋势:智能化与云化的深度融合

随着AI、云计算与5G技术的快速发展,IC工具虚拟机正朝着更智能、更高效的方向演进:

AI驱动的资源调度

结合机器学习算法,虚拟机可分析历史任务负载,预测资源需求,实现智能化的动态调度,通过强化学习优化仿真任务的CPU与内存分配,进一步提升资源利用率。

边缘计算与虚拟机轻量化

针对边缘设备(如IoT芯片)的快速设计需求,轻量级虚拟机(如容器化虚拟机)将逐渐普及,降低资源开销,实现“设计-验证-部署”的一体化闭环。

安全增强与可信执行

基于硬件虚拟化技术(如Intel SGX、AMD SEV),虚拟机将支持“可信执行环境”(TEE),确保设计数据在计算过程中的机密性与完整性,抵御侧信道攻击等安全威胁。

开源生态与标准化

以OpenStack、KVM为代表的开源虚拟化平台将与IC工具链深度整合,推动虚拟机接口与部署流程的标准化,降低企业对商业虚拟化方案的依赖,促进产业生态的开放与创新。

IC工具虚拟机通过虚拟化技术重构了IC设计与验证的运行模式,不仅提升了资源效率与设计质量,更推动了半导体产业的云化与协同发展,随着AI、边缘计算等技术的持续赋能,虚拟机将进一步深化其在IC全生命周期中的应用,成为支撑未来芯片创新的核心引擎,对于半导体企业而言,拥抱虚拟化技术已不再是“选择题”,而是提升竞争力的必然路径。